- SIMPLE FPGA SIMULATION WAVEFORM HOW TO

- SIMPLE FPGA SIMULATION WAVEFORM VERIFICATION

- SIMPLE FPGA SIMULATION WAVEFORM SOFTWARE

- SIMPLE FPGA SIMULATION WAVEFORM CODE

- SIMPLE FPGA SIMULATION WAVEFORM ISO

SIMPLE FPGA SIMULATION WAVEFORM SOFTWARE

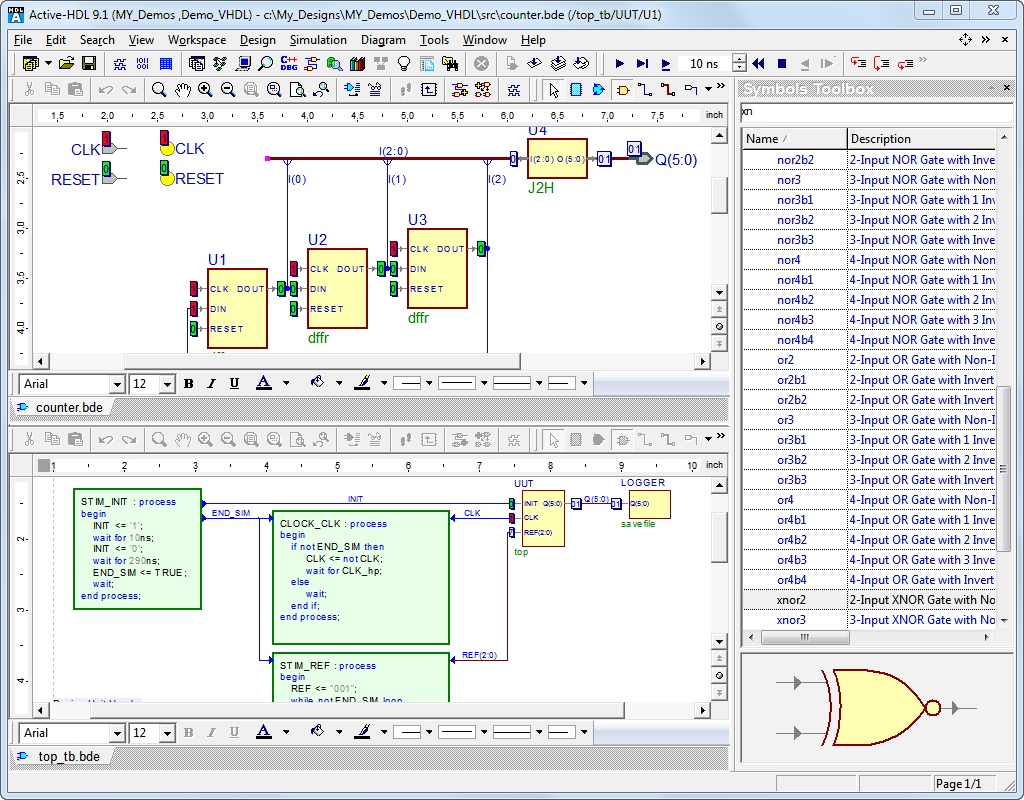

These use models enable many applications such as hardware and software co-verification utilizing TLM wrappers and high-speed AXI or AHB bus transactors to connect design residing in hardware with Virtual Platforms.

SIMPLE FPGA SIMULATION WAVEFORM VERIFICATION

HES-DVM™ provides verification teams with multiple use modes including both emulation and physical prototyping techniques enabling SoC teams to work on a single platform.Įmulation modes include simulation acceleration, transaction level co-emulation and in-circuit emulation for chip and system level verification of SoC and ASIC designs.

SIMPLE FPGA SIMULATION WAVEFORM CODE

Working concurrently with one another they develop and verify high-level code with RTL accuracy and speed-effective SoC emulation or prototyping models reducing test time and a risk of silicon re-spins. Utilizing the latest co-emulation standards like SCE-MI or TLM and newest FPGA technology, hardware and software design teams obtain early access to the hardware prototype of the design. HDL Coder can generate scripts and projects for RTL synthesis, and it has integrated with synthesis and implementation tools from Xilinx, Intel, and Microsemi to provide automated FPGA programming workflows.HES-DVM™ is a fully automated and scalable hybrid verification environment for SoC and ASIC designs. Many are available as Hardware Support Packages, or from your FPGA board vendor. You will still need a reference design for HDL Coder to plug your algorithm into for FPGA programming.

SIMPLE FPGA SIMULATION WAVEFORM ISO

Once you have a hardware-ready design, HDL Coder™ generates target-independent Verilog or VHDL RTL with links back to the model for debugging and traceability for functional safety workflows such as DO-254 and ISO 26262. A best practice is to simulate this version of your design and compare the results with your golden algorithm results. Simulink offers a time-based visual environment for hardware architecture design.

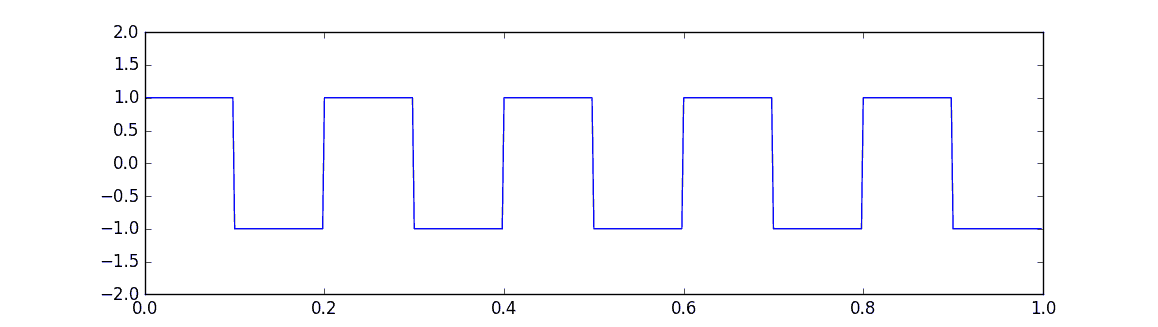

You will need to adapt your algorithms to add hardware architecture to process a continuous stream of data, typically with fixed-point data types. The major steps for FPGA programming with MATLAB and Simulink are:

If you model your algorithms in MATLAB and Simulink, you can focus on designing the algorithm and hardware architecture. Most of the time this is due to problems in the design step that were not identified in the verification step.įPGA Programming with MATLAB and Simulink

SIMPLE FPGA SIMULATION WAVEFORM HOW TO

The first few tries often involve figuring out why it does not work and how to fix it. After FPGA programming, you can run using real input or test input. This produces the bitstream that is loaded onto the device for FPGA programming. This is the process of determining which physical resources on the FPGA to program with which logic, and how to connect (route) them. Your design will need to plug into this “reference design.” An SoC FPGA also has dedicated registers that both the hardware and software can use to communicate with each other. An FPGA contains a lot of dedicated resources already-the pins, the clock signal, input/output processing such as analog-to-digital converters (ADC), and interfaces to off-chip memory and other devices on the board. This technology transforms the RTL to digital logic gates and attempts to meet your register-to-register clock frequency goals while minimizing use of the resources on the FPGA. This can be as simple as a VHDL or Verilog testbench commercial projects typically use a methodology such as the Universal Verification Methodology ( UVM). This step ensures that the design works as intended before FPGA programming. The goal is to match the functionality of the algorithm while operating on a continuous stream of data, using fixed-point operations for efficiency. This is the process of creating the hardware logic itself, typically by writing register-transfer logic (RTL) using a hardware description language (HDL) such as VHDL ® or Verilog ®. In the case of an SoC FPGA, the hardware-software SoC architecture.

0 kommentar(er)

0 kommentar(er)